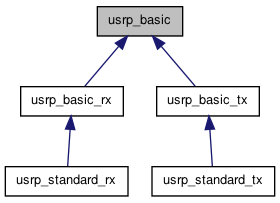

abstract base class for usrp operations More...

#include <usrp_basic.h>

Public Member Functions | |

| virtual | ~usrp_basic () |

| std::vector< std::vector < db_base_sptr > > | db () const |

| std::vector< db_base_sptr > | db (int which_side) |

| bool | is_valid (const usrp_subdev_spec &ss) |

| is the subdev_spec valid? | |

| db_base_sptr | selected_subdev (const usrp_subdev_spec &ss) |

| given a subdev_spec, return the corresponding daughterboard object. | |

| long | fpga_master_clock_freq () const |

| return frequency of master oscillator on USRP | |

| void | set_fpga_master_clock_freq (long master_clock) |

| int | usb_data_rate () const |

| void | set_verbose (bool on) |

| bool | write_eeprom (int i2c_addr, int eeprom_offset, const std::string buf) |

| Write EEPROM on motherboard or any daughterboard. | |

| std::string | read_eeprom (int i2c_addr, int eeprom_offset, int len) |

| Read EEPROM on motherboard or any daughterboard. | |

| bool | write_i2c (int i2c_addr, const std::string buf) |

| Write to I2C peripheral. | |

| std::string | read_i2c (int i2c_addr, int len) |

| Read from I2C peripheral. | |

| bool | set_adc_offset (int which_adc, int offset) |

| Set ADC offset correction. | |

| bool | set_dac_offset (int which_dac, int offset, int offset_pin) |

| Set DAC offset correction. | |

| bool | set_adc_buffer_bypass (int which_adc, bool bypass) |

| Control ADC input buffer. | |

| bool | set_dc_offset_cl_enable (int bits, int mask) |

| Enable/disable automatic DC offset removal control loop in FPGA. | |

| std::string | serial_number () |

| return the usrp's serial number. | |

| virtual int | daughterboard_id (int which_side) const =0 |

| Return daughterboard ID for given side [0,1]. | |

| bool | write_atr_tx_delay (int value) |

| Clock ticks to delay rising of T/R signal. | |

| bool | write_atr_rx_delay (int value) |

| Clock ticks to delay falling edge of T/R signal. | |

| bool | common_set_pga (txrx_t txrx, int which_amp, double gain_in_db) |

| Set Programmable Gain Amplifier(PGA) | |

| double | common_pga (txrx_t txrx, int which_amp) const |

| Return programmable gain amplifier gain setting in dB. | |

| double | common_pga_min (txrx_t txrx) const |

| Return minimum legal PGA gain in dB. | |

| double | common_pga_max (txrx_t txrx) const |

| Return maximum legal PGA gain in dB. | |

| double | common_pga_db_per_step (txrx_t txrx) const |

| Return hardware step size of PGA(linear in dB). | |

| bool | _common_write_oe (txrx_t txrx, int which_side, int value, int mask) |

| Write direction register(output enables) for pins that go to daughterboard. | |

| bool | common_write_io (txrx_t txrx, int which_side, int value, int mask) |

| Write daughterboard i/o pin value. | |

| bool | common_read_io (txrx_t txrx, int which_side, int *value) |

| Read daughterboard i/o pin value. | |

| int | common_read_io (txrx_t txrx, int which_side) |

| Read daughterboard i/o pin value. | |

| bool | common_write_refclk (txrx_t txrx, int which_side, int value) |

| Write daughterboard refclk config register. | |

| bool | common_write_atr_mask (txrx_t txrx, int which_side, int value) |

| Automatic Transmit/Receive switching. | |

| bool | common_write_atr_txval (txrx_t txrx, int which_side, int value) |

| bool | common_write_atr_rxval (txrx_t txrx, int which_side, int value) |

| bool | common_write_aux_dac (txrx_t txrx, int which_side, int which_dac, int value) |

| Write auxiliary digital to analog converter. | |

| bool | common_read_aux_adc (txrx_t txrx, int which_side, int which_adc, int *value) |

| Read auxiliary analog to digital converter. | |

| int | common_read_aux_adc (txrx_t txrx, int which_side, int which_adc) |

| Read auxiliary analog to digital converter. | |

| virtual bool | set_pga (int which_amp, double gain_in_db)=0 |

| Set Programmable Gain Amplifier (PGA) | |

| virtual double | pga (int which_amp) const =0 |

| Return programmable gain amplifier gain setting in dB. | |

| virtual double | pga_min () const =0 |

| Return minimum legal PGA gain in dB. | |

| virtual double | pga_max () const =0 |

| Return maximum legal PGA gain in dB. | |

| virtual double | pga_db_per_step () const =0 |

| Return hardware step size of PGA (linear in dB). | |

| virtual bool | _write_oe (int which_side, int value, int mask)=0 |

| Write direction register (output enables) for pins that go to daughterboard. | |

| virtual bool | write_io (int which_side, int value, int mask)=0 |

| Write daughterboard i/o pin value. | |

| virtual bool | read_io (int which_side, int *value)=0 |

| Read daughterboard i/o pin value. | |

| virtual int | read_io (int which_side)=0 |

| Read daughterboard i/o pin value. | |

| virtual bool | write_refclk (int which_side, int value)=0 |

| Write daughterboard refclk config register. | |

| virtual bool | write_atr_mask (int which_side, int value)=0 |

| virtual bool | write_atr_txval (int which_side, int value)=0 |

| virtual bool | write_atr_rxval (int which_side, int value)=0 |

| virtual bool | write_aux_dac (int which_side, int which_dac, int value)=0 |

| Write auxiliary digital to analog converter. | |

| virtual bool | read_aux_adc (int which_side, int which_adc, int *value)=0 |

| Read auxiliary analog to digital converter. | |

| virtual int | read_aux_adc (int which_side, int which_adc)=0 |

| Read auxiliary analog to digital converter. | |

| virtual int | block_size () const =0 |

| returns current fusb block size | |

| virtual long | converter_rate () const =0 |

| returns A/D or D/A converter rate in Hz | |

| bool | _set_led (int which_led, bool on) |

| bool | _write_fpga_reg (int regno, int value) |

| Write FPGA register. | |

| bool | _read_fpga_reg (int regno, int *value) |

| Read FPGA register. | |

| int | _read_fpga_reg (int regno) |

| Read FPGA register. | |

| bool | _write_fpga_reg_masked (int regno, int value, int mask) |

| Write FPGA register with mask. | |

| bool | _write_9862 (int which_codec, int regno, unsigned char value) |

| Write AD9862 register. | |

| bool | _read_9862 (int which_codec, int regno, unsigned char *value) const |

| Read AD9862 register. | |

| int | _read_9862 (int which_codec, int regno) const |

| Read AD9862 register. | |

| bool | _write_spi (int optional_header, int enables, int format, std::string buf) |

| Write data to SPI bus peripheral. | |

| std::string | _read_spi (int optional_header, int enables, int format, int len) |

| bool | start () |

| Start data transfers. Called in base class to derived class order. | |

| bool | stop () |

| Stop data transfers. Called in base class to derived class order. | |

Static Public Attributes | |

| static const int | READ_FAILED = -99999 |

| magic value used on alternate register read interfaces | |

Protected Member Functions | |

| void | shutdown_daughterboards () |

| void | init_db (usrp_basic_sptr u) |

| One time call, made only only from usrp_standard_*::make after shared_ptr is created. | |

| usrp_basic (int which_board, libusb_device_handle *open_interface(libusb_device *dev), const std::string fpga_filename="", const std::string firmware_filename="") | |

| void | set_usb_data_rate (int usb_data_rate) |

| advise usrp_basic of usb data rate (bytes/sec) | |

| bool | _write_aux_dac (int slot, int which_dac, int value) |

| Write auxiliary digital to analog converter. | |

| bool | _read_aux_adc (int slot, int which_adc, int *value) |

| Read auxiliary analog to digital converter. | |

| int | _read_aux_adc (int slot, int which_adc) |

| Read auxiliary analog to digital converter. | |

Protected Attributes | |

| libusb_device_handle * | d_udh |

| struct libusb_context * | d_ctx |

| int | d_usb_data_rate |

| int | d_bytes_per_poll |

| bool | d_verbose |

| long | d_fpga_master_clock_freq |

| unsigned int | d_fpga_shadows [MAX_REGS] |

| int | d_dbid [2] |

| std::vector< std::vector < db_base_sptr > > | d_db |

Static Protected Attributes | |

| static const int | MAX_REGS = 128 |

Detailed Description

abstract base class for usrp operations

Constructor & Destructor Documentation

| usrp_basic::usrp_basic | ( | int | which_board, |

| libusb_device_handle * | open_interfacelibusb_device *dev, | ||

| const std::string | fpga_filename = "", |

||

| const std::string | firmware_filename = "" |

||

| ) | [protected] |

| virtual usrp_basic::~usrp_basic | ( | ) | [virtual] |

Member Function Documentation

Write direction register(output enables) for pins that go to daughterboard.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which size value value to write into register mask which bits of value to write into reg

Each d'board has 16-bits of general purpose i/o. Setting the bit makes it an output from the FPGA to the d'board.

This register is initialized based on a value stored in the d'board EEPROM. In general, you shouldn't be using this routine without a very good reason. Using this method incorrectly will kill your USRP motherboard and/or daughterboard.

| bool usrp_basic::_read_9862 | ( | int | which_codec, |

| int | regno, | ||

| unsigned char * | value | ||

| ) | const |

Read AD9862 register.

- Parameters:

-

which_codec 0 or 1 regno 6-bit register number value 8-bit value

- Returns:

- true iff successful

| int usrp_basic::_read_9862 | ( | int | which_codec, |

| int | regno | ||

| ) | const |

Read AD9862 register.

- Parameters:

-

which_codec 0 or 1 regno 6-bit register number

- Returns:

- register value if successful, else READ_FAILED

| bool usrp_basic::_read_aux_adc | ( | int | slot, |

| int | which_adc, | ||

| int * | value | ||

| ) | [protected] |

Read auxiliary analog to digital converter.

- Parameters:

-

slot 2-bit slot number. E.g., SLOT_TX_A which_adc [0,1] value return 12-bit value [0,4095]

- Returns:

- true iff successful

| int usrp_basic::_read_aux_adc | ( | int | slot, |

| int | which_adc | ||

| ) | [protected] |

Read auxiliary analog to digital converter.

- Parameters:

-

slot 2-bit slot number. E.g., SLOT_TX_A which_adc [0,1]

- Returns:

- value in the range [0,4095] if successful, else READ_FAILED.

| int usrp_basic::_read_fpga_reg | ( | int | regno | ) |

Read FPGA register.

- Parameters:

-

regno 7-bit register number

- Returns:

- register value if successful, else READ_FAILED

| bool usrp_basic::_read_fpga_reg | ( | int | regno, |

| int * | value | ||

| ) |

Read FPGA register.

- Parameters:

-

regno 7-bit register number value 32-bit value

- Returns:

- true iff successful

| std::string usrp_basic::_read_spi | ( | int | optional_header, |

| int | enables, | ||

| int | format, | ||

| int | len | ||

| ) |

| bool usrp_basic::_write_9862 | ( | int | which_codec, |

| int | regno, | ||

| unsigned char | value | ||

| ) |

Write AD9862 register.

- Parameters:

-

which_codec 0 or 1 regno 6-bit register number value 8-bit value

- Returns:

- true iff successful

| bool usrp_basic::_write_aux_dac | ( | int | slot, |

| int | which_dac, | ||

| int | value | ||

| ) | [protected] |

Write auxiliary digital to analog converter.

- Parameters:

-

slot Which Tx or Rx slot to write. N.B., SLOT_TX_A and SLOT_RX_A share the same AUX DAC's. SLOT_TX_B and SLOT_RX_B share the same AUX DAC's. which_dac [0,3] RX slots must use only 0 and 1. TX slots must use only 2 and 3. value [0,4095]

- Returns:

- true iff successful

| bool usrp_basic::_write_fpga_reg | ( | int | regno, |

| int | value | ||

| ) |

Write FPGA register.

- Parameters:

-

regno 7-bit register number value 32-bit value

- Returns:

- true iff successful

| bool usrp_basic::_write_fpga_reg_masked | ( | int | regno, |

| int | value, | ||

| int | mask | ||

| ) |

Write FPGA register with mask.

- Parameters:

-

regno 7-bit register number value 16-bit value mask 16-bit value

- Returns:

- true if successful Only use this for registers who actually implement a mask in the verilog firmware, like FR_RX_MASTER_SLAVE

| virtual bool usrp_basic::_write_oe | ( | int | which_side, |

| int | value, | ||

| int | mask | ||

| ) | [pure virtual] |

Write direction register (output enables) for pins that go to daughterboard.

- Parameters:

-

which_side [0,1] which size value value to write into register mask which bits of value to write into reg

Each d'board has 16-bits of general purpose i/o. Setting the bit makes it an output from the FPGA to the d'board.

This register is initialized based on a value stored in the d'board EEPROM. In general, you shouldn't be using this routine without a very good reason. Using this method incorrectly will kill your USRP motherboard and/or daughterboard.

Implemented in usrp_basic_rx, and usrp_basic_tx.

| bool usrp_basic::_write_spi | ( | int | optional_header, |

| int | enables, | ||

| int | format, | ||

| std::string | buf | ||

| ) |

Write data to SPI bus peripheral.

- Parameters:

-

optional_header 0,1 or 2 bytes to write before buf. enables bitmask of peripherals to write. See usrp_spi_defs.h format transaction format. See usrp_spi_defs.h SPI_FMT_* buf the data to write

- Returns:

- true iff successful Writes are limited to a maximum of 64 bytes.

If format specifies that optional_header bytes are present, they are written to the peripheral immediately prior to writing buf.

| virtual int usrp_basic::block_size | ( | ) | const [pure virtual] |

returns current fusb block size

Implemented in usrp_basic_rx, and usrp_basic_tx.

| double usrp_basic::common_pga | ( | txrx_t | txrx, |

| int | which_amp | ||

| ) | const |

Return programmable gain amplifier gain setting in dB.

- Parameters:

-

txrx Tx or Rx? which_amp which amp [0,3]

| double usrp_basic::common_pga_db_per_step | ( | txrx_t | txrx | ) | const |

Return hardware step size of PGA(linear in dB).

- Parameters:

-

txrx Tx or Rx?

| double usrp_basic::common_pga_max | ( | txrx_t | txrx | ) | const |

Return maximum legal PGA gain in dB.

- Parameters:

-

txrx Tx or Rx?

| double usrp_basic::common_pga_min | ( | txrx_t | txrx | ) | const |

Return minimum legal PGA gain in dB.

- Parameters:

-

txrx Tx or Rx?

Read auxiliary analog to digital converter.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board which_adc [0,1] value return 12-bit value [0,4095]

- Returns:

- true iff successful

| int usrp_basic::common_read_aux_adc | ( | txrx_t | txrx, |

| int | which_side, | ||

| int | which_adc | ||

| ) |

Read auxiliary analog to digital converter.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board which_adc [0,1]

- Returns:

- value in the range [0,4095] if successful, else READ_FAILED.

Read daughterboard i/o pin value.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board value output

| int usrp_basic::common_read_io | ( | txrx_t | txrx, |

| int | which_side | ||

| ) |

Read daughterboard i/o pin value.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board

- Returns:

- register value if successful, else READ_FAILED

Set Programmable Gain Amplifier(PGA)

- Parameters:

-

txrx Tx or Rx? which_amp which amp [0,3] gain_in_db gain value(linear in dB)

gain is rounded to closest setting supported by hardware.

- Returns:

- true iff sucessful.

- See also:

- pga_min(), pga_max(), pga_db_per_step()

Automatic Transmit/Receive switching.

If automatic transmit/receive (ATR) switching is enabled in the FR_ATR_CTL register, the presence or absence of data in the FPGA transmit fifo selects between two sets of values for each of the 4 banks of daughterboard i/o pins.

Each daughterboard slot has 3 16-bit registers associated with it: FR_ATR_MASK_*, FR_ATR_TXVAL_* and FR_ATR_RXVAL_*

FR_ATR_MASK_{0,1,2,3}: These registers determine which of the daugherboard i/o pins are

affected by ATR switching. If a bit in the mask is set, the

corresponding i/o bit is controlled by ATR, else it's output

value comes from the normal i/o pin output register:

FR_IO_{0,1,2,3}. FR_ATR_TXVAL_{0,1,2,3}:

FR_ATR_RXVAL_{0,1,2,3}:If the Tx fifo contains data, then the bits from TXVAL that are selected by MASK are output. Otherwise, the bits from RXVAL that are selected by MASK are output.

Write auxiliary digital to analog converter.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board N.B., SLOT_TX_A and SLOT_RX_A share the same AUX DAC's. SLOT_TX_B and SLOT_RX_B share the same AUX DAC's. which_dac [2,3] TX slots must use only 2 and 3. value [0,4095]

- Returns:

- true iff successful

Write daughterboard i/o pin value.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board value value to write into register mask which bits of value to write into reg

Write daughterboard refclk config register.

- Parameters:

-

txrx Tx or Rx? which_side [0,1] which d'board value value to write into register, see below

Control whether a reference clock is sent to the daughterboards, and what frequency. The refclk is sent on d'board i/o pin 0.

3 2 1 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 +-----------------------------------------------+-+------------+ | Reserved (Must be zero) |E| DIVISOR | +-----------------------------------------------+-+------------+

Bit 7 -- 1 turns on refclk, 0 allows IO use Bits 6:0 Divider value

| virtual long usrp_basic::converter_rate | ( | ) | const [pure virtual] |

returns A/D or D/A converter rate in Hz

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual int usrp_basic::daughterboard_id | ( | int | which_side | ) | const [pure virtual] |

Return daughterboard ID for given side [0,1].

- Parameters:

-

which_side [0,1] which daughterboard

- Returns:

- daughterboard id >= 0 if successful

- -1 if no daugherboard

- -2 if invalid EEPROM on daughterboard

Implemented in usrp_basic_rx, and usrp_basic_tx.

| std::vector<db_base_sptr> usrp_basic::db | ( | int | which_side | ) |

Return a vector of size >= 1 that contains shared pointers to the daughterboard instance(s) associated with the specified side.

- Parameters:

-

which_side [0,1] which daughterboard

It is an error to use the returned objects after the usrp_basic object has been destroyed.

| std::vector<std::vector<db_base_sptr> > usrp_basic::db | ( | ) | const [inline] |

Return a vector of vectors that contain shared pointers to the daughterboard instance(s) associated with the specified side.

It is an error to use the returned objects after the usrp_basic object has been destroyed.

References d_db.

| long usrp_basic::fpga_master_clock_freq | ( | ) | const [inline] |

return frequency of master oscillator on USRP

References d_fpga_master_clock_freq.

Referenced by usrp_basic_tx::converter_rate(), and usrp_basic_rx::converter_rate().

| void usrp_basic::init_db | ( | usrp_basic_sptr | u | ) | [protected] |

One time call, made only only from usrp_standard_*::make after shared_ptr is created.

| bool usrp_basic::is_valid | ( | const usrp_subdev_spec & | ss | ) |

is the subdev_spec valid?

| virtual double usrp_basic::pga | ( | int | which_amp | ) | const [pure virtual] |

Return programmable gain amplifier gain setting in dB.

- Parameters:

-

which_amp which amp [0,3]

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual double usrp_basic::pga_db_per_step | ( | ) | const [pure virtual] |

Return hardware step size of PGA (linear in dB).

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual double usrp_basic::pga_max | ( | ) | const [pure virtual] |

Return maximum legal PGA gain in dB.

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual double usrp_basic::pga_min | ( | ) | const [pure virtual] |

Return minimum legal PGA gain in dB.

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual bool usrp_basic::read_aux_adc | ( | int | which_side, |

| int | which_adc, | ||

| int * | value | ||

| ) | [pure virtual] |

Read auxiliary analog to digital converter.

- Parameters:

-

which_side [0,1] which d'board which_adc [0,1] value return 12-bit value [0,4095]

- Returns:

- true iff successful

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual int usrp_basic::read_aux_adc | ( | int | which_side, |

| int | which_adc | ||

| ) | [pure virtual] |

Read auxiliary analog to digital converter.

- Parameters:

-

which_side [0,1] which d'board which_adc [0,1]

- Returns:

- value in the range [0,4095] if successful, else READ_FAILED.

Implemented in usrp_basic_rx, and usrp_basic_tx.

| std::string usrp_basic::read_eeprom | ( | int | i2c_addr, |

| int | eeprom_offset, | ||

| int | len | ||

| ) |

Read EEPROM on motherboard or any daughterboard.

- Parameters:

-

i2c_addr I2C bus address of EEPROM eeprom_offset byte offset in EEPROM to begin reading len number of bytes to read

- Returns:

- the data read if successful, else a zero length string.

| std::string usrp_basic::read_i2c | ( | int | i2c_addr, |

| int | len | ||

| ) |

Read from I2C peripheral.

- Parameters:

-

i2c_addr I2C bus address (7-bits) len number of bytes to read

- Returns:

- the data read if successful, else a zero length string. Reads are limited to a maximum of 64 bytes.

| virtual bool usrp_basic::read_io | ( | int | which_side, |

| int * | value | ||

| ) | [pure virtual] |

Read daughterboard i/o pin value.

- Parameters:

-

which_side [0,1] which d'board value output

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual int usrp_basic::read_io | ( | int | which_side | ) | [pure virtual] |

Read daughterboard i/o pin value.

- Parameters:

-

which_side [0,1] which d'board

- Returns:

- register value if successful, else READ_FAILED

Implemented in usrp_basic_rx, and usrp_basic_tx.

| db_base_sptr usrp_basic::selected_subdev | ( | const usrp_subdev_spec & | ss | ) |

given a subdev_spec, return the corresponding daughterboard object.

- Exceptions:

-

std::invalid_ argument if ss is invalid.

- Parameters:

-

ss specifies the side and subdevice

| std::string usrp_basic::serial_number | ( | ) |

return the usrp's serial number.

- Returns:

- non-zero length string iff successful.

Control ADC input buffer.

- Parameters:

-

which_adc which ADC[0,3] bypass if non-zero, bypass input buffer and connect input directly to switched cap SHA input of RxPGA.

| bool usrp_basic::set_adc_offset | ( | int | which_adc, |

| int | offset | ||

| ) |

Set ADC offset correction.

- Parameters:

-

which_adc which ADC[0,3]: 0 = RX_A I, 1 = RX_A Q... offset 16-bit value to subtract from raw ADC input.

| bool usrp_basic::set_dac_offset | ( | int | which_dac, |

| int | offset, | ||

| int | offset_pin | ||

| ) |

Set DAC offset correction.

- Parameters:

-

which_dac which DAC[0,3]: 0 = TX_A I, 1 = TX_A Q... offset 10-bit offset value (ambiguous format: See AD9862 datasheet). offset_pin 1-bit value. If 0 offset applied to -ve differential pin; If 1 offset applied to +ve differential pin.

| bool usrp_basic::set_dc_offset_cl_enable | ( | int | bits, |

| int | mask | ||

| ) |

Enable/disable automatic DC offset removal control loop in FPGA.

- Parameters:

-

bits which control loops to enable mask which bitsto pay attention to

If the corresponding bit is set, enable the automatic DC offset correction control loop.

The 4 low bits are significant:

ADC0 = (1 << 0) ADC1 = (1 << 1) ADC2 = (1 << 2) ADC3 = (1 << 3)

By default the control loop is enabled on all ADC's.

| void usrp_basic::set_fpga_master_clock_freq | ( | long | master_clock | ) | [inline] |

Tell API that the master oscillator on the USRP is operating at a non-standard fixed frequency. This is only needed for custom USRP hardware modified to operate at a different frequency from the default factory configuration. This function must be called prior to any other API function.

- Parameters:

-

master_clock USRP2 FPGA master clock frequency in Hz (10..64 MHz)

References d_fpga_master_clock_freq.

| virtual bool usrp_basic::set_pga | ( | int | which_amp, |

| double | gain_in_db | ||

| ) | [pure virtual] |

Set Programmable Gain Amplifier (PGA)

- Parameters:

-

which_amp which amp [0,3] gain_in_db gain value (linear in dB)

gain is rounded to closest setting supported by hardware.

- Returns:

- true iff sucessful.

- See also:

- pga_min(), pga_max(), pga_db_per_step()

Implemented in usrp_basic_rx, and usrp_basic_tx.

| void usrp_basic::set_usb_data_rate | ( | int | usb_data_rate | ) | [protected] |

advise usrp_basic of usb data rate (bytes/sec)

N.B., this doesn't tweak any hardware. Derived classes should call this to inform us of the data rate whenever it's first set or if it changes.

- Parameters:

-

usb_data_rate bytes/sec

| void usrp_basic::shutdown_daughterboards | ( | ) | [protected] |

| bool usrp_basic::start | ( | ) |

Start data transfers. Called in base class to derived class order.

Reimplemented in usrp_basic_rx, usrp_basic_tx, usrp_standard_rx, and usrp_standard_tx.

| bool usrp_basic::stop | ( | ) |

Stop data transfers. Called in base class to derived class order.

Reimplemented in usrp_basic_rx, usrp_basic_tx, usrp_standard_rx, and usrp_standard_tx.

| int usrp_basic::usb_data_rate | ( | ) | const [inline] |

- Returns:

- usb data rate in bytes/sec

References d_usb_data_rate.

| virtual bool usrp_basic::write_atr_mask | ( | int | which_side, |

| int | value | ||

| ) | [pure virtual] |

Implemented in usrp_basic_rx, and usrp_basic_tx.

| bool usrp_basic::write_atr_rx_delay | ( | int | value | ) |

Clock ticks to delay falling edge of T/R signal.

- See also:

- write_atr_mask, write_atr_txval, write_atr_rxval

| virtual bool usrp_basic::write_atr_rxval | ( | int | which_side, |

| int | value | ||

| ) | [pure virtual] |

Implemented in usrp_basic_rx, and usrp_basic_tx.

| bool usrp_basic::write_atr_tx_delay | ( | int | value | ) |

Clock ticks to delay rising of T/R signal.

- See also:

- write_atr_mask, write_atr_txval, write_atr_rxval

| virtual bool usrp_basic::write_atr_txval | ( | int | which_side, |

| int | value | ||

| ) | [pure virtual] |

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual bool usrp_basic::write_aux_dac | ( | int | which_side, |

| int | which_dac, | ||

| int | value | ||

| ) | [pure virtual] |

Write auxiliary digital to analog converter.

- Parameters:

-

which_side [0,1] which d'board N.B., SLOT_TX_A and SLOT_RX_A share the same AUX DAC's. SLOT_TX_B and SLOT_RX_B share the same AUX DAC's. which_dac [2,3] TX slots must use only 2 and 3. value [0,4095]

- Returns:

- true iff successful

Implemented in usrp_basic_rx, and usrp_basic_tx.

| bool usrp_basic::write_eeprom | ( | int | i2c_addr, |

| int | eeprom_offset, | ||

| const std::string | buf | ||

| ) |

Write EEPROM on motherboard or any daughterboard.

- Parameters:

-

i2c_addr I2C bus address of EEPROM eeprom_offset byte offset in EEPROM to begin writing buf the data to write

- Returns:

- true iff sucessful

| bool usrp_basic::write_i2c | ( | int | i2c_addr, |

| const std::string | buf | ||

| ) |

Write to I2C peripheral.

- Parameters:

-

i2c_addr I2C bus address (7-bits) buf the data to write

- Returns:

- true iff successful Writes are limited to a maximum of of 64 bytes.

| virtual bool usrp_basic::write_io | ( | int | which_side, |

| int | value, | ||

| int | mask | ||

| ) | [pure virtual] |

Write daughterboard i/o pin value.

- Parameters:

-

which_side [0,1] which d'board value value to write into register mask which bits of value to write into reg

Implemented in usrp_basic_rx, and usrp_basic_tx.

| virtual bool usrp_basic::write_refclk | ( | int | which_side, |

| int | value | ||

| ) | [pure virtual] |

Write daughterboard refclk config register.

- Parameters:

-

which_side [0,1] which d'board value value to write into register, see below

Control whether a reference clock is sent to the daughterboards, and what frequency. The refclk is sent on d'board i/o pin 0.

3 2 1 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 +-----------------------------------------------+-+------------+ | Reserved (Must be zero) |E| DIVISOR | +-----------------------------------------------+-+------------+

Bit 7 -- 1 turns on refclk, 0 allows IO use Bits 6:0 Divider value

Implemented in usrp_basic_rx, and usrp_basic_tx.

Member Data Documentation

int usrp_basic::d_bytes_per_poll [protected] |

struct libusb_context* usrp_basic::d_ctx [protected] |

std::vector< std::vector<db_base_sptr> > usrp_basic::d_db [protected] |

Shared pointers to subclasses of db_base.

The outer vector is of length 2 (0 = side A, 1 = side B). The inner vectors are of length 1, 2 or 3 depending on the number of subdevices implemented by the daugherboard. At this time, only the Basic Rx and LF Rx implement more than 1 subdevice.

Referenced by db().

int usrp_basic::d_dbid[2] [protected] |

Referenced by usrp_basic_tx::daughterboard_id(), and usrp_basic_rx::daughterboard_id().

long usrp_basic::d_fpga_master_clock_freq [protected] |

Referenced by fpga_master_clock_freq(), and set_fpga_master_clock_freq().

unsigned int usrp_basic::d_fpga_shadows[MAX_REGS] [protected] |

libusb_device_handle* usrp_basic::d_udh [protected] |

int usrp_basic::d_usb_data_rate [protected] |

Referenced by usb_data_rate().

bool usrp_basic::d_verbose [protected] |

Referenced by set_verbose().

const int usrp_basic::MAX_REGS = 128 [static, protected] |

const int usrp_basic::READ_FAILED = -99999 [static] |

magic value used on alternate register read interfaces

The documentation for this class was generated from the following file: