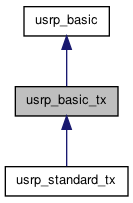

class for accessing the transmit side of the USRP More...

#include <usrp_basic.h>

Public Member Functions | |

| ~usrp_basic_tx () | |

| bool | set_fpga_tx_sample_rate_divisor (unsigned int div) |

| tell the fpga the rate tx samples are going to the D/A's | |

| int | write (const void *buf, int len, bool *underrun) |

| Write data to the A/D's via the FPGA. | |

| void | wait_for_completion () |

| virtual long | converter_rate () const |

| sampling rate of D/A converter | |

| long | dac_rate () const |

| int | daughterboard_id (int which_side) const |

| Return daughterboard ID for given side [0,1]. | |

| bool | set_pga (int which_amp, double gain_in_db) |

| Set Programmable Gain Amplifier (PGA) | |

| double | pga (int which_amp) const |

| Return programmable gain amplifier gain setting in dB. | |

| double | pga_min () const |

| Return minimum legal PGA gain in dB. | |

| double | pga_max () const |

| Return maximum legal PGA gain in dB. | |

| double | pga_db_per_step () const |

| Return hardware step size of PGA (linear in dB). | |

| bool | _write_oe (int which_side, int value, int mask) |

| Write direction register (output enables) for pins that go to daughterboard. | |

| bool | write_io (int which_side, int value, int mask) |

| Write daughterboard i/o pin value. | |

| bool | read_io (int which_side, int *value) |

| Read daughterboard i/o pin value. | |

| int | read_io (int which_side) |

| Read daughterboard i/o pin value. | |

| bool | write_refclk (int which_side, int value) |

| Write daughterboard refclk config register. | |

| bool | write_atr_mask (int which_side, int value) |

| bool | write_atr_txval (int which_side, int value) |

| bool | write_atr_rxval (int which_side, int value) |

| bool | write_aux_dac (int which_side, int which_dac, int value) |

| Write auxiliary digital to analog converter. | |

| bool | read_aux_adc (int which_side, int which_adc, int *value) |

| Read auxiliary analog to digital converter. | |

| int | read_aux_adc (int which_side, int which_adc) |

| Read auxiliary analog to digital converter. | |

| int | block_size () const |

| returns current fusb block size | |

| bool | start () |

| Start data transfers. Called in base class to derived class order. | |

| bool | stop () |

| Stop data transfers. Called in base class to derived class order. | |

Static Public Member Functions | |

| static usrp_basic_tx * | make (int which_board, int fusb_block_size=0, int fusb_nblocks=0, const std::string fpga_filename="", const std::string firmware_filename="") |

| invokes constructor, returns instance or 0 if trouble | |

Protected Member Functions | |

| usrp_basic_tx (int which_board, int fusb_block_size=0, int fusb_nblocks=0, const std::string fpga_filename="", const std::string firmware_filename="") | |

| bool | set_tx_enable (bool on) |

| bool | tx_enable () const |

| bool | disable_tx () |

| void | restore_tx (bool on) |

| void | probe_tx_slots (bool verbose) |

Detailed Description

class for accessing the transmit side of the USRP

Constructor & Destructor Documentation

| usrp_basic_tx::usrp_basic_tx | ( | int | which_board, |

| int | fusb_block_size = 0, |

||

| int | fusb_nblocks = 0, |

||

| const std::string | fpga_filename = "", |

||

| const std::string | firmware_filename = "" |

||

| ) | [protected] |

- Parameters:

-

which_board Which USRP board on usb (not particularly useful; use 0) fusb_block_size fast usb xfer block size. Must be a multiple of 512. Use zero for a reasonable default. fusb_nblocks number of fast usb URBs to allocate. Use zero for a reasonable default. fpga_filename name of file that contains image to load into FPGA firmware_filename name of file that contains image to load into FX2

| usrp_basic_tx::~usrp_basic_tx | ( | ) |

Member Function Documentation

| bool usrp_basic_tx::_write_oe | ( | int | which_side, |

| int | value, | ||

| int | mask | ||

| ) | [virtual] |

Write direction register (output enables) for pins that go to daughterboard.

- Parameters:

-

which_side [0,1] which size value value to write into register mask which bits of value to write into reg

Each d'board has 16-bits of general purpose i/o. Setting the bit makes it an output from the FPGA to the d'board.

This register is initialized based on a value stored in the d'board EEPROM. In general, you shouldn't be using this routine without a very good reason. Using this method incorrectly will kill your USRP motherboard and/or daughterboard.

Implements usrp_basic.

| int usrp_basic_tx::block_size | ( | ) | const [virtual] |

returns current fusb block size

Implements usrp_basic.

| virtual long usrp_basic_tx::converter_rate | ( | ) | const [inline, virtual] |

sampling rate of D/A converter

Implements usrp_basic.

References usrp_basic::fpga_master_clock_freq().

Referenced by dac_rate().

| long usrp_basic_tx::dac_rate | ( | ) | const [inline] |

References converter_rate().

| int usrp_basic_tx::daughterboard_id | ( | int | which_side | ) | const [inline, virtual] |

Return daughterboard ID for given side [0,1].

- Parameters:

-

which_side [0,1] which daughterboard

- Returns:

- daughterboard id >= 0 if successful

- -1 if no daugherboard

- -2 if invalid EEPROM on daughterboard

Implements usrp_basic.

References usrp_basic::d_dbid.

| bool usrp_basic_tx::disable_tx | ( | ) | [protected] |

| static usrp_basic_tx* usrp_basic_tx::make | ( | int | which_board, |

| int | fusb_block_size = 0, |

||

| int | fusb_nblocks = 0, |

||

| const std::string | fpga_filename = "", |

||

| const std::string | firmware_filename = "" |

||

| ) | [static] |

invokes constructor, returns instance or 0 if trouble

- Parameters:

-

which_board Which USRP board on usb (not particularly useful; use 0) fusb_block_size fast usb xfer block size. Must be a multiple of 512. Use zero for a reasonable default. fusb_nblocks number of fast usb URBs to allocate. Use zero for a reasonable default. fpga_filename name of file that contains image to load into FPGA firmware_filename name of file that contains image to load into FX2

| double usrp_basic_tx::pga | ( | int | which_amp | ) | const [virtual] |

Return programmable gain amplifier gain setting in dB.

- Parameters:

-

which_amp which amp [0,3]

Implements usrp_basic.

| double usrp_basic_tx::pga_db_per_step | ( | ) | const [virtual] |

Return hardware step size of PGA (linear in dB).

Implements usrp_basic.

| double usrp_basic_tx::pga_max | ( | ) | const [virtual] |

Return maximum legal PGA gain in dB.

Implements usrp_basic.

| double usrp_basic_tx::pga_min | ( | ) | const [virtual] |

Return minimum legal PGA gain in dB.

Implements usrp_basic.

| void usrp_basic_tx::probe_tx_slots | ( | bool | verbose | ) | [protected] |

| bool usrp_basic_tx::read_aux_adc | ( | int | which_side, |

| int | which_adc, | ||

| int * | value | ||

| ) | [virtual] |

Read auxiliary analog to digital converter.

- Parameters:

-

which_side [0,1] which d'board which_adc [0,1] value return 12-bit value [0,4095]

- Returns:

- true iff successful

Implements usrp_basic.

| int usrp_basic_tx::read_aux_adc | ( | int | which_side, |

| int | which_adc | ||

| ) | [virtual] |

Read auxiliary analog to digital converter.

- Parameters:

-

which_side [0,1] which d'board which_adc [0,1]

- Returns:

- value in the range [0,4095] if successful, else READ_FAILED.

Implements usrp_basic.

| bool usrp_basic_tx::read_io | ( | int | which_side, |

| int * | value | ||

| ) | [virtual] |

Read daughterboard i/o pin value.

- Parameters:

-

which_side [0,1] which d'board value output

Implements usrp_basic.

| int usrp_basic_tx::read_io | ( | int | which_side | ) | [virtual] |

Read daughterboard i/o pin value.

- Parameters:

-

which_side [0,1] which d'board

- Returns:

- register value if successful, else READ_FAILED

Implements usrp_basic.

| void usrp_basic_tx::restore_tx | ( | bool | on | ) | [protected] |

| bool usrp_basic_tx::set_fpga_tx_sample_rate_divisor | ( | unsigned int | div | ) |

tell the fpga the rate tx samples are going to the D/A's

div = fpga_master_clock_freq () * 2

sample_rate is determined by a myriad of registers in the 9862. That's why you have to tell us, so we can tell the fpga.

| bool usrp_basic_tx::set_pga | ( | int | which_amp, |

| double | gain_in_db | ||

| ) | [virtual] |

Set Programmable Gain Amplifier (PGA)

- Parameters:

-

which_amp which amp [0,3] gain_in_db gain value (linear in dB)

gain is rounded to closest setting supported by hardware.

- Returns:

- true iff sucessful.

- See also:

- pga_min(), pga_max(), pga_db_per_step()

Implements usrp_basic.

| bool usrp_basic_tx::start | ( | ) |

Start data transfers. Called in base class to derived class order.

Reimplemented from usrp_basic.

Reimplemented in usrp_standard_tx.

| bool usrp_basic_tx::stop | ( | ) |

Stop data transfers. Called in base class to derived class order.

Reimplemented from usrp_basic.

Reimplemented in usrp_standard_tx.

| bool usrp_basic_tx::tx_enable | ( | ) | const [inline, protected] |

| void usrp_basic_tx::wait_for_completion | ( | ) |

| int usrp_basic_tx::write | ( | const void * | buf, |

| int | len, | ||

| bool * | underrun | ||

| ) |

Write data to the A/D's via the FPGA.

len must be a multiple of 512 bytes.

- Returns:

- number of bytes written or -1 on error.

if underrun is non-NULL, it will be set to true iff a transmit underrun condition is detected.

| bool usrp_basic_tx::write_atr_mask | ( | int | which_side, |

| int | value | ||

| ) | [virtual] |

Implements usrp_basic.

| bool usrp_basic_tx::write_atr_rxval | ( | int | which_side, |

| int | value | ||

| ) | [virtual] |

Implements usrp_basic.

| bool usrp_basic_tx::write_atr_txval | ( | int | which_side, |

| int | value | ||

| ) | [virtual] |

Implements usrp_basic.

| bool usrp_basic_tx::write_aux_dac | ( | int | which_side, |

| int | which_dac, | ||

| int | value | ||

| ) | [virtual] |

Write auxiliary digital to analog converter.

- Parameters:

-

which_side [0,1] which d'board N.B., SLOT_TX_A and SLOT_RX_A share the same AUX DAC's. SLOT_TX_B and SLOT_RX_B share the same AUX DAC's. which_dac [2,3] TX slots must use only 2 and 3. value [0,4095]

- Returns:

- true iff successful

Implements usrp_basic.

| bool usrp_basic_tx::write_io | ( | int | which_side, |

| int | value, | ||

| int | mask | ||

| ) | [virtual] |

Write daughterboard i/o pin value.

- Parameters:

-

which_side [0,1] which d'board value value to write into register mask which bits of value to write into reg

Implements usrp_basic.

| bool usrp_basic_tx::write_refclk | ( | int | which_side, |

| int | value | ||

| ) | [virtual] |

Write daughterboard refclk config register.

- Parameters:

-

which_side [0,1] which d'board value value to write into register, see below

Control whether a reference clock is sent to the daughterboards, and what frequency. The refclk is sent on d'board i/o pin 0.

3 2 1 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0 +-----------------------------------------------+-+------------+ | Reserved (Must be zero) |E| DIVISOR | +-----------------------------------------------+-+------------+

Bit 7 -- 1 turns on refclk, 0 allows IO use Bits 6:0 Divider value

Implements usrp_basic.

The documentation for this class was generated from the following file: